AP/BB、Controller用フリップチップボンディング高密度パッケージ基板

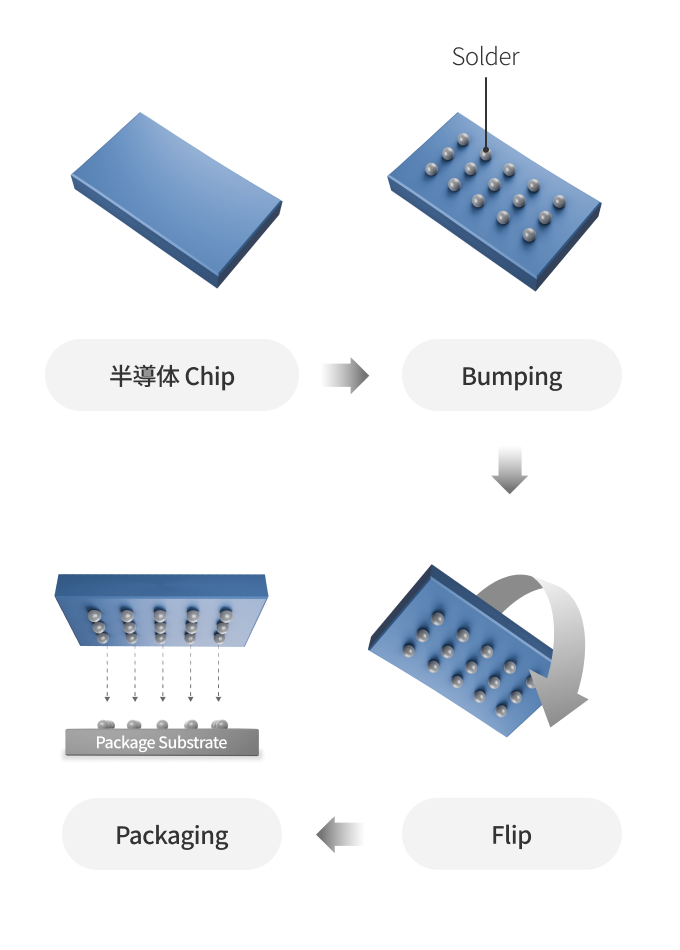

半導体にワイヤボンディングによる接合ではなく、バンプを用いて反転させた状態で基板に接続することから、FCCSP(Flip Chip Chip Scale Package)と言います。主に、モバイルIT機器のAP(Application Processor)などの高性能半導体に使われます。また、金線を使うWBCSPに比べ、電気的信号の移動経路が短く、多くのインプット/アウトプットを形成できるため、高密度半導体に対応可能です。

主なコア技術

Bumping 構造図

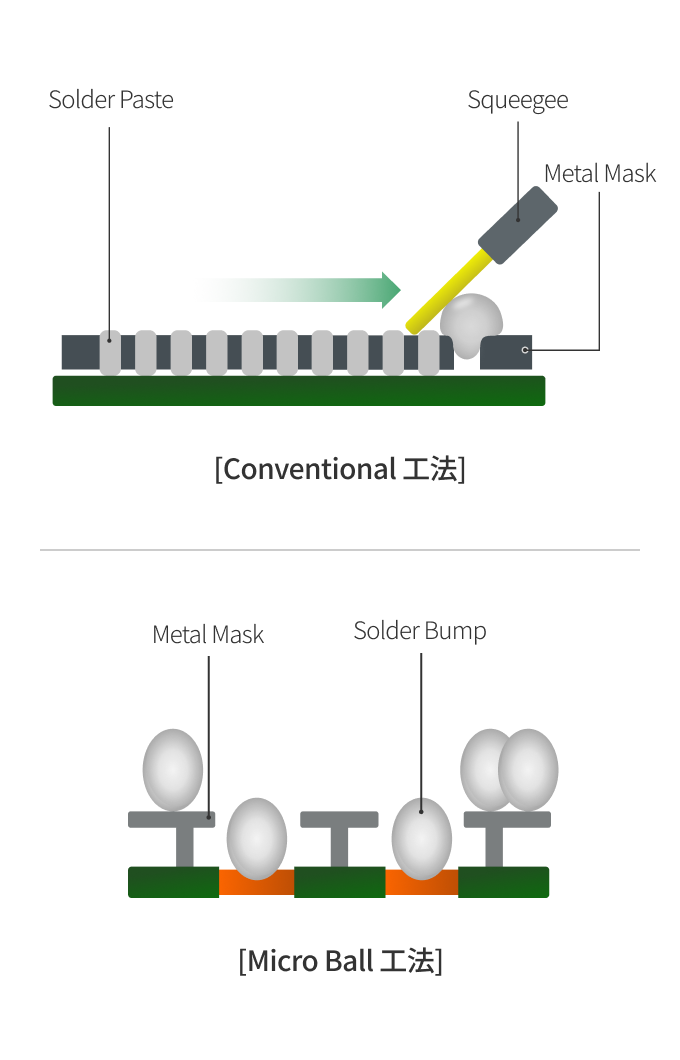

Micro Ball Bump 工法

- Available for Fine Bump Pitch

- Good for Small Bump Risk

- Good Quality for Bump Characteristics

基板の種類

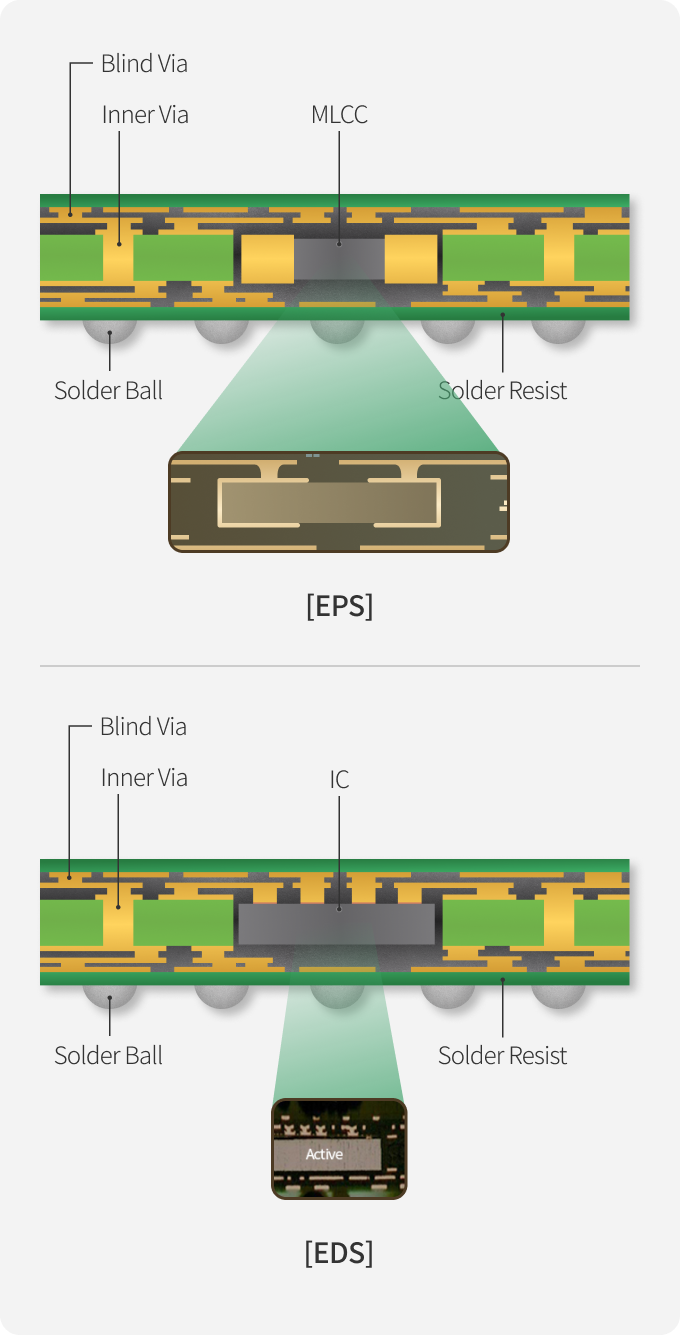

EPS & EDS (Embedded Passive Substrate & Embedded Die Substrate)

EPS/EDSは、半導体の受動素子やICなどを基板内部に内装した基板です。受動素子は通常、Power Supply Voltage Levelの安定化に使います。ICを基板の内部に内装すると、パッケージのサイズや厚みを削減できます。

ETS (Embedded Trace Substrate)

ETSは、最外殻回路のパターンが絶縁材に埋め込まれた形の回路基板です。基板はCoreless構造で、コストが上がることなく微細回路を実現できるため、レイヤーダウン設計が容易(4L→3L)になっています。また、エッチング工程がパターンの幅に影響しないため、回路の幅を精密に制御できます。

FCCSP Lineup

Lineup by Specification

| Routing Density | Build-Up Line Width / Space | 7 / 8um (Mass Production) | 6 / 7um (Sample Available) |

|---|---|---|---|

| BVH / Pad Registration | 40 / 67um (Mass Production) | 37 / 60um (Sample Available) | |

| SRO Diameter SR Registration | 45 ± 10um (Mass Production) | 40 ± 10um (Sample Available) | |

| FC Bump Pitch (Peripheral) | 40um (Mass Production) | 35um (Sample Available) | |

| FC Bump Pitch (Area) | 90um (Mass Production) | 80um (Sample Available) | |

| Low Z-Height | Core / PPG Thickness | 40 / 18um (Mass Production) | 35 / 15um (Sample Available) |

| SR Thickness | 10 ± 4um (Mass Production) | 8 ± 3um (Sample Available) |

* umは、㎛を意味します。