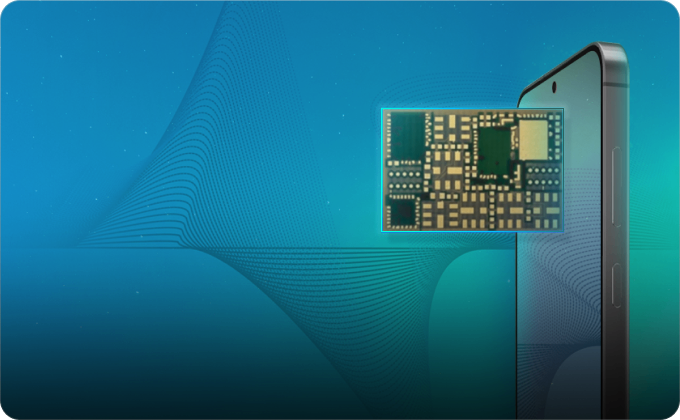

국내 최대 반도체 기판 기업

패키지 기판(Package Substrate)은 모바일과 PC의 핵심 반도체에 사용되고 있으며, 반도체와 메인보드 간 전기적 신호 전달 역할 및 고가의 반도체를 외부 스트레스로부터 보호해주는 역할을 하고 있습니다. 일반 기판 보다 훨씬 더 미세한 회로가 형성되어 있는 고밀도 회로 기판으로, 고가의 반도체를 직접 메인 기판에 부착하게 될 때 발생하는 조립 불량과 비용을 줄일 수 있습니다.

Solutions

-

- FCCSP

- 반도체에 와이어 본딩을 통한 접합이 아닌 범프를 통해 뒤집어진 채로 기판과 연결되며 주로 모바일 IT 기기의 AP(Application Processor) 등 고성능 반도체에 사용됩니다.

-

- WBCSP

- Gold Wire로 반도체 칩과 패키지 기판을 연결하고, 반도체 Chip 크기가 기판 면적의 80% 넘는 제품입니다.

-

- SiP

- Package 안에 여러 개의 IC와 Passive Component가 실장 되어 복합적인 기능을 하나의 System으로 구현하는 제품으로 방열 특성을 가지고 있습니다.

-

- FCBGA

- 고집적 반도체 칩을 메인보드와 연결하기 위한 고밀도 패키지 기판입니다. 반도체 칩과 패키지 기판을 Flip Chip Bump로 연결합니다.

FAQ

-

당사 Substrate 생산 기지로는 국내 2곳 (세종, 부산)과 해외 1곳 (베트남)이 있습니다.

-

PC, 게임기부터 Data Center, 자동차 등 다양한 분야에서 사용됩니다.

- Client: Desktop, Note PC용 CPU 및 GPU, Game Console용 SoC

- HPC: Server용 CPU, AI 가속기용 ASIC

- Network: Router/Switch용 ASIC

- Automotive: ADAS, Radar 및 Infotainment 용 SoC

-

고객지원 > 고객문의 화면에서 제품문의로 기술 및 구매 문의를 할 수 있도록 되어 있습니다.

-

삼성전기는 FCBGA의 표면 처리로 OSP 및 ENEPIG 공법을 주로 제공하고 있으나 필요시 새로운 표면처리 공법의 개발 및 대응도 가능합니다.

-

BGA 제품의 경우 주로 ENEPIG, Ni/Au, Direct Au 등의 공법을 제공하고 있으며 전해 Ni/Au는 Thick Ni/Au 과 Thin Ni/Au 로 구분할 수 있습니다.