시스템 구현이 가능한

패키지 기판

Package 안에 여러 개의 IC와 Passive Component가 실장 되어 복합적인 기능을 하나의 System으로 구현하는 제품입니다. 또한 PA(Power Amplifier)와 같은 제품에 사용되어, 방열 특성을 가지고 있습니다. 제품 시리즈로는 Flip-Chip SiP와 Coreless가 있습니다.

소형화

여러 개의 IC 및 수동소자가 하나의 Module에 통합되어 Package 소형화 구현이 가능합니다.

![SiP 부품 구성요소. [1.Substrate, 2.Die1, 3.Die2, 4.Die3]](/resources/images/kr/product/sip_sec_title_img01.png)

얇은 박판 구현

초 박판 구동성 확보로 0.2mm 두께 기판(6층 기준) 구현이 가능합니다.

![SiP의 특징인 얇은 박판 구현을 설명하기 위한 두께별로 기판의 단면도. [0.2T 6L RF-SiP(200um), 0.27T 8L RF-SiP(270um), 10L ~, 5G 안테나 모듈]](/resources/images/kr/product/sip_sec_title_img02.png)

주요핵심기술

Coreless RF-SiP

Coreless 공법으로 절연 두께를 낮추어 EMI(Electro Magnetic Interference) 및 Parasitic Inductance를 제어하여 신호 특성을 향상시킬 수 있으며, 이를 기반으로 Thin Substrate를 구현할 수 있습니다.

![Coreless 공법을 이용해 절연두께를 낮춘 Coreless 기판과 Cored 기판의 단면도 비교. [Cored 기판(45um core), Coreless 기판(20um dielectric) *Thin substrate 구현 가능]](/resources/images/kr/product/sip_sec01_img01.png)

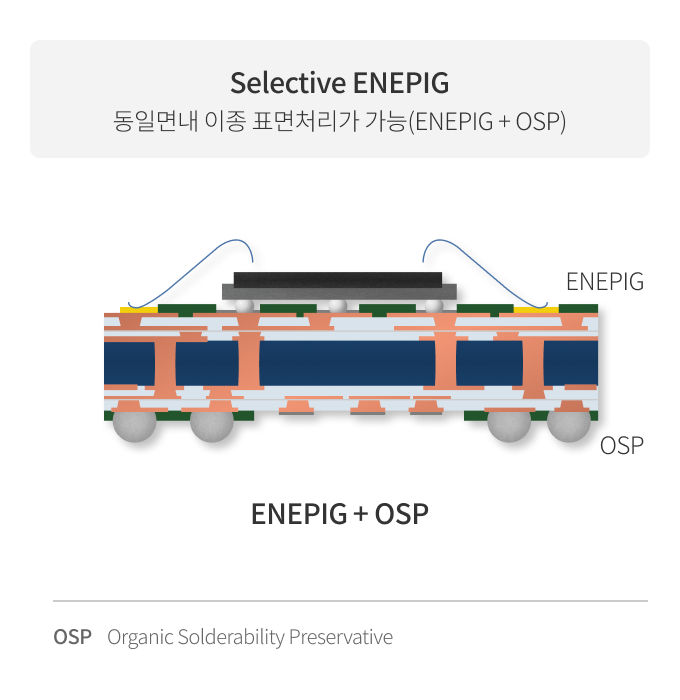

ENEPIG 표면 처리

ENEPIG 표면 처리 기술은 아래와 같은 특성을 가지고 있습니다.

![ENIG/ENEPIG(Gold, Nickel, Copper, Palladium) 와 Thin Ni ENEPIG(Gold, Nickel, Palladium, Copper) 두께 차이 비교. [ENIG/ENEPIG(Ni 두께: 5~6.5um) , Thin Ni ENEPIG(Ni 두께: 0.1um)]](/resources/images/kr/product/sip_sec01_img02.png)

SiP Lineup

Lineup by Specification

| Layer Structure | Cored | 2L / 4L / 6L / 8L / 10L (Mass Production) | + 12L / 14L (Sample Available) |

|---|---|---|---|

| Coreless | 5L / 6L / 7L / 8L (Mass Production) | + 4L / 9L / 10L (Sample Available) | |

| Line Width / Space | 12 / 16um (Mass Production) | 10 / 15um (Sample Available) | |

| Bump Pitch | 130um (Mass Production) | 105um (Sample Available) | |

| Surface Finish | Direct Au, Thin ENEPIG, Selective ENEPIG (Mass Production) | Direct Au, Thin ENEPIG, Selective ENEPIG (Sample Available) | |

* um은 ㎛을 의미합니다.